BEN ABDALLAH Abderazek

Professor, Regent (Dean of the Undergraduate school)

- Affiliation

- Department of Computer Science and Engineering/Division of Computer Engineering

- Title

- Professor, Regent (Dean of the Undergraduate school)

- benab@u-aizu.ac.jp

Education

- Courses - Undergraduate

- Computer Architecture, Undergraduate level, UoA, 2018 – present

- Introduction to Computer Systems, Undergraduate level, UoA, 2018 – present

- Parallel Computer Systems, Undergraduate level, UoA, 2018 – present

- Computer System Engineering, UoA, 2008-2018

- Embedded Systems, UoA, 2008-2016

- Logic Circuit Design Exercises, UoA, 2008-2018

- Computer Architecture Exercises, UoA, 2008-2018

- Courses - Graduate

- Neuromorphic Computing, UoA, 2023 – present

- Embedded Real-Time Systems, UoA, 2008 – 2022

- Multicore Computing, UoA, 2010-2015

- Advanced Computer Organization, UoA, 2008 – 2023

Research

- Specialization

-

Communication and network engineering

Computer system

High performance computing

Intelligent informatics

- Educational Background, Biography

-

- 1999.4-2002.3 Ph.D. in Computer Engineering, National Univ. of Electro-communications at Tokyo

- 2002.4-2007.3 Research Associate, National Univ. of Electro-communications, Tokyo

- 2007.4-2007.9 Assistant Professor, National Univ. of Electro-communications, Tokyo

- 2007.10-2011.3 Assistant Professor, UoA

- 2011.4-2012.3 Associate Professor, UoA

- 2012.4-2014.3 Senior Associate Professor, UoA

- 2014.4-present Professor, UoA

- 2014.4-2022.03 Head, Computer Engineering Division, UoA

- 2014.4-present Member, Education and Research Council, UoA

- 2022.4 ~ Present Director, Department of Computer Science and Engineering, UoA

- 2022.4-present Dean, School of Computer Science and Engineering, UoA

- 2022.4-present Regent, The University of Aizu

Invited Lecturer:- 2010-2013 Visiting Professor, Department of Computer Science and Engineering, Hong Kong University of Science and Technology, Hong Kong, China

- 2011-2015 Visiting Professor, School of Software Engineering, Huazhong University of Science and Technology, Wuhan, China

- 2022 - present Lecturer, Graduate School of Science and Technology, Kyoto Institute of Technology, Kyoto, Japan

- 2023 - present, Tokyo University of Foreign Studies, Tokyo, Japan

- Current Research Theme

Abderazek Ben Abdallah's research is dedicated to advancing energy-efficient, high-performance computing systems, with a particular emphasis on digital signal processing workloads constrained by computational, network, and reliability challenges. His work in neuromorphic AI circuits and systems encompasses energy-efficient learning algorithms and AI-chip hardware development, driving advancements in low-power computing, adaptive intelligence and real-time processing for embedded applications. He has also contributed to the advancement of on-chip interconnects, particularly fault-tolerant 3D-NoCs/ICs (SiPh, Hybrid), designed to optimize system efficiency. Additionally, his research enhances the reliability of integrated circuits and SoCs by tackling key challenges like thermal management and error mitigation. His algorithms and systems have been instrumental in advancing numerous emerging applications and have been patented across multiple innovations through collaborations with various industrial partners.

- Key Topic

- Neuromorphic AI Circuits and Systems; On-chip Interconnects (2D/3D, Si-Photonics, Hybrid); Emerging Applications; Low-power Computing, Adaptive Intelligence; Real-time; Sustainable; Anthropomorphic Android

- Affiliated Academic Society

- Member of Sigma Xi, the Scientific Research Honor Society, 2025-

- IEEE Senior Member since 2014

- ACM Senior Member since 2016

- Member of IEEE Circuits and Systems

- Member of the European Alliance for Innovation

Major Journal Editorial Board:- Associate Editor, IEEE Computer Magazine, 2025~

- Associate Editor, IEEE Network Magazine, 2025~2027

- Associate Editor, Neuromorphic Engineering, Frontiers in Neuroscience, 2025~

- Guest Editor for the IEEE Transactions on Emerging Topics in Computing (2014)

Main research

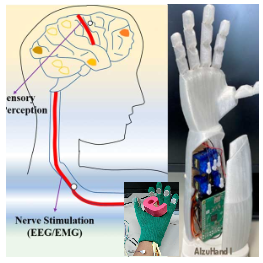

- Adaptive Anthropomorphic Android

-

We are actively researching anthropomorphic prosthetics and androids, integrating cutting-edge neuroscience, artificial intelligence, and robotics to develop highly responsive, lifelike systems that enhance both human mobility and interaction. Through neuromorphic computing and spiking neural networks, we strive to achieve more natural, intuitive control, ensuring seamless communication between artificial limbs, androids, and biological systems.

Our focus on non-invasive neural interfaces enables prosthetics to adapt dynamically to user intent, enhancing precision, comfort, and fluidity of motion. Meanwhile, our research on advanced sensory processing for androids aims to equip robotic entities with human-like awareness, allowing them to engage in complex tasks, interpret environmental stimuli, and interact intelligently with users. By bridging the gap between biomechanical engineering and AI-driven cognition, we are paving the way for next-generation assistive technologies and autonomous systems that are deeply integrated into daily life. Our work contributes to advancements in rehabilitation, human augmentation, and adaptive robotics, revolutionizing the way artificial systems complement and extend human capabilities.

...read more

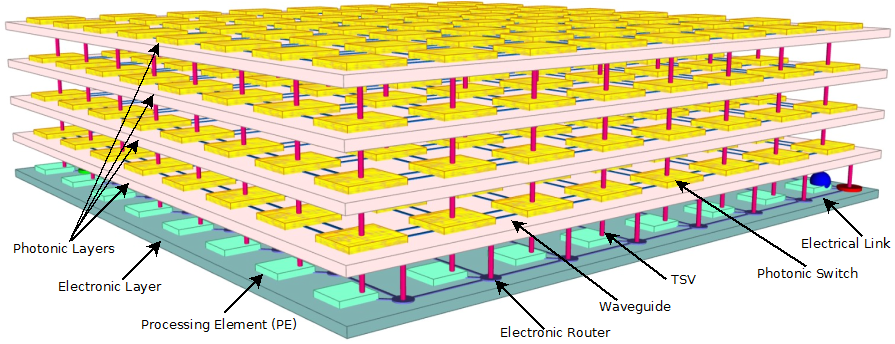

- Advanced of On-Chip Interconnects (3D-NoCs/ICs (SiPh, Hybrid))

-

Complex SoCs contain dozens of components made of processor cores, DSPs, memory, accelerators, and I/O, all integrated into a single die area of just a few square millimeters. Such complex systems will be interconnected via a complex on-chip interconnect closer to a sophisticated network than current bus-based solutions. This network must provide high throughput and low latency while keeping area and power consumption low. Our research effort is about solving several design challenges to enable such new paradigm in massively parallel many-core systems. In particular, we are investigating fault-tolerance, 3D-TSV integration, photonic communication, low-power mapping techniques, and low-latency adaptive routing.

...read more

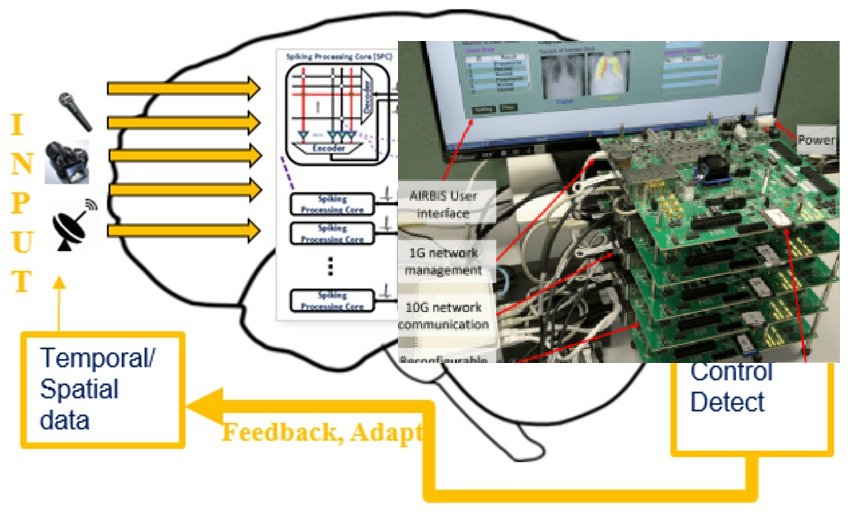

- Neuromorphic AI Circuits and Systems

-

We are exploring the development of an adaptive ultra-low power neuromorphic chip (NASH) and systems, enhanced by our previously developed fault-tolerant three-dimensional on-chip interconnect technology. The NASH system boasts several features, including an efficient adaptive configuration method that enables the reconfiguration of various SNN parameters such as spike weights, routing, hidden layers, and topology. Additionally, the system incorporates a blend of different deep neural network topologies, an efficient fault-tolerant multicast spike routing algorithm, and an effective on-chip learning mechanism. To demonstrate the performance of the NASH system, we will develop an FPGA implementation and establish a VLSI implementation. The ultimate goal of NASH is to bring brain-inspired processing technology to small-scale embedded sensors and sensor-based devices, such as BCI (EEG/EMG), audio, presence detection, and activity recognition.

...read more